About This Course

Front end VLSI design can’t get easier than this

Do you want to build just verilog models or high-quality verilog models in half the time?

Have you implemented a processor using Verilog? Which was the most important part of your implementation? What was your code size in Verilog? What if, we told you that you can reduce your verilog code size by about 3.5x by a new technology? What if, we told you that you can create any digital sequential logic you can dream up faster than you ever thought possible, all within your browser?

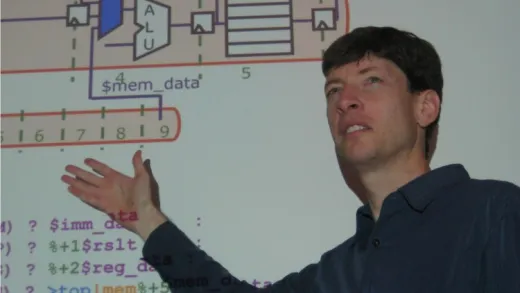

How about a ‘change’? Change the way you used to write your verilog code. Change the way you used to implement Pipelining for your processor. Change is the only “constant”. I encourage and welcome you to think in the right direction with experts from this field in my webinar on “Pipelining RISC-V with Transaction-Level Verilog” which was conducted on 10th Feb’ 2018 with Steve Hoover, Founder of Redwood EDA and Makerchip Platform

This webinar is really important for people

who have taken up my RISC-V ISA course on Udemy, as we will show

efficient RTL implementation of some instructions in this

one.

Enjoy the webinar and Happy Learning....

Students will be able to use and implement concepts of pipelining using TL-verilog language and Makerchip platform

Build their own verilog models for IP's using a simpler and powerful Verilog design environment

Nguyen L.

It's mostly review for me since I have designing/verifying ASIC for decades now. I want to teach my son TL-Verilog.